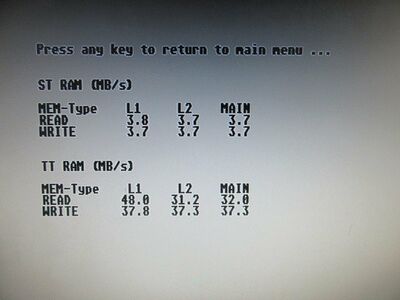

MemSpeed (Falcon)

Description: MEMSPEED checks the available bandwidth of the 1st level cache, the 2nd level cache and the mainboard memory.

Version: 1.0

Resolutions: Medium / High

Format: PRG

Language: English

Link: File:MEMSPEED.zip

Medium Resolution

| This article is only a english draft copy (Stub). If you can, help us now to improve it. - The complete list of stubs is in this category |

Need better / more images.

MEMSPEED V1.0 ½ 1994 by Torsten Lang MEMSPEED measures the maximum achievable data throughput for the following cases: CPU->L1 Cache, CPU->L2 Cache, CPU->MEM, L1 Cache->CPU, L2 Cache->CPU, MEM->CPU Depending on the processor, the actual memory bandwidth is not always achieved. Although it could be determined using some tricks, the test would then be less practical. Theoretically, a 68030 clocked at 50MHz in burst mode should read 100MB/s within the L1 Cache (longword accesses), but in practice, it turns out to be only half of that. There may be dead times (2 cycles between two memory accesses) when transferring register lists (e.g., MOVEM.L (SP)+,A0-A6/D0-D7). Even if the 68030 fills its internal (=L1) cache at 100MB/s in burst mode, this speed cannot be sustained in practice but can be achieved momentarily in certain limit situations. This test aims to help assess the quality of Turbo/Fast RAM cards. As far as I know, there is no such program for Atari computers. Benchmarks often provide unrealistically high values because they usually run in the cache (L1 or L2). A few words about the terms L1 Cache and L2 Cache: L1 Cache (or 1st Level Cache) is the processor's internal cache memory (you should already know what Cache Memory is). The 68020 has only an instruction cache (hence this program won't find an L1 Cache for it), while the 68030 has an additional data cache. This fast cache is organized into cache lines of 4 longwords (totaling 256 bytes for 020, 2*256 bytes for 030; I currently have no data for 040 or 060, but the cache is significantly larger there). L2 Cache (or 2nd Level Cache) is located on the Turbo card or the computer's motherboard, but not within the processor. Its speed is usually between that of the main memory and L1 Cache. The sizes of the caches are not currently measured; instead, the program assumes the following sizes: L1 < 16KB L2 < 512KB If there are processors or Turbos in the future that exceed these values, MEMSPEED will provide incorrect values. Furthermore, I assume that there will not be cards with more than 999MB/s bandwidth anytime soon. To keep the program compact, it is entirely written in assembler. I have largely avoided safety or plausibility checks so far. Since the _hz_200 counter serves as a timer, IRQs must remain active during the measurement so that the measured data may be slightly lower than the actual values, especially at high values. However, the determined values should be reasonably accurate. My advice: Test the computer as raw as possible, without multitasking, etc. The MEMSPEED program may only be distributed in conjunction with this text. Furthermore, distribution via PD distributors and other commercial providers is prohibited! If the program is to be distributed in connection with a commercial product, my written consent is required, otherwise, it will violate applicable law. The following companies currently have my permission to distribute this program: MW electronic, K”nigswinter MESA electronic, Lindhorst If you have received this program from another source along with a commercial product or found it on a PD diskette, etc., please contact me immediately. I also welcome any feedback (postcard) with information about the results and your computer configuration. Finally, the most important: I assume no liability for any damages, of any kind, that may arise from using this program. Bad Nauheim, November 1994